## ECE 342 Electronic Circuits

# Lecture 33 CMOS Characteristics

Jose E. Schutt-Aine

Electrical & Computer Engineering

University of Illinois

jesa@Illinois.edu

## **Digital Circuits**

$V_{IH}$ : Input voltage at high state  $\rightarrow V_{IHmin}$

$V_{IL}$ : Input voltage at low state  $\rightarrow V_{ILmax}$

$V_{OH}$ : Output voltage at high state  $\rightarrow V_{OHmin}$

$V_{OL}$ : Output voltage at low state  $\rightarrow V_{OLmin}$

Likewise for current we can define

Currents into input

$$I_{IH} \longleftrightarrow I_{IHmax}$$

$I_{II} \longleftrightarrow I_{II max}$

Currents into output

$$I_{OH} \longleftrightarrow I_{OHmax}$$

$I_{OL} \longleftrightarrow I_{OLmax}$

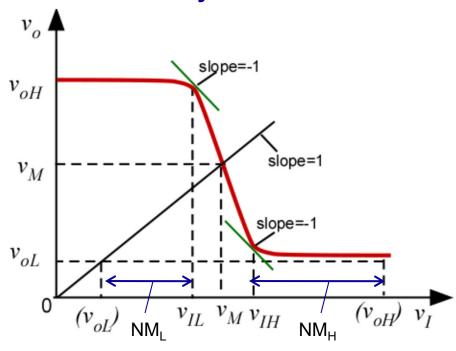

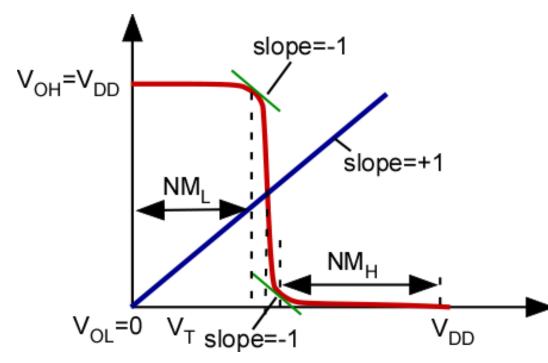

## **Voltage Transfer Characteristics (VTC)**

The static operation of a logic circuit is determined by its VTC

In low state: noise margin is NM<sub>L</sub>

$$NM_L = V_{IL} - V_{OL}$$

• In high state: noise margin is  $NM_H$

$$NM_H = V_{OH} - V_{IH}$$

An ideal VTC will maximize noise margins

$V_{IL}$  and  $V_{IH}$  are the points where the slope of the VTC=-1

Optimum:

$$NM_L = NM_H = V_{DD} / 2$$

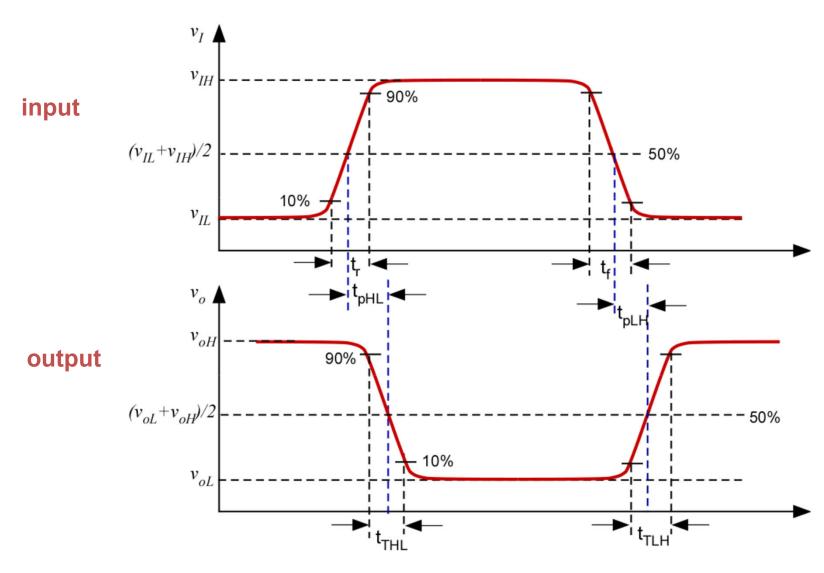

## **Switching Time & Propagation Delay**

## **Switching Time & Propagation Delay**

$t_r$ =rise time (from 10% to 90%)  $t_f$ =fall time (from 90% to 10%)  $t_{pLH}$ =low-to-high propagation delay  $t_{pHL}$ =high-to-low propagation delay

Inverter propagation delay:

$$t_p = \frac{1}{2} \left( t_{pLH} + t_{pHL} \right)$$

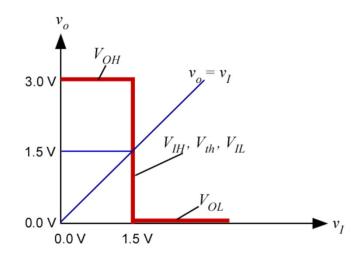

## **VTC** and Noise Margins

For a logic-circuit family employing a 3-V supply, suggest an ideal set of values for  $V_{th}$ ,  $V_{IL}$ ,  $V_{IH}$ ,  $V_{OH}$ ,  $NM_L$ ,  $NM_H$ . Also, sketch the VTC. What value of voltage gain in the transition region does your ideal specification imply?

#### **Ideal 3V logic implies:**

$$V_{OH} = V_{DD} = 3.0V;$$

$V_{OL} = 0.0V$

$$V_{th} = V_{DD} / 2 = 3.0 / 2 = 1.5V;$$

$$V_{IL} = V_{DD} / 2 = 1.5V$$

;  $V_{IH} = V_{DD} / 2 = 1.5V$

### **VTC** and Noise Margins

$$NM_H = V_{OH} - V_{IH} = 3.0 - 1.5 = 1.5V$$

$$NM_L = V_{IL} - V_{OL} = 1.5 - 0.0 = 1.5V$$

**Inverting transfer characteristics**

#### The gain in the transition region is:

$$(V_{OH} - V_{OL}) / (V_{IH} - V_{IL}) = (3.0 - 0.0) / (1.5 - 1.5)$$

$$=3/0=\infty V/V$$

## **CMOS Noise Margins**

When inverter threshold is at  $V_{DD}/2$ , the noise margin  $NM_H$  and  $NM_L$  are equalized

$$NM_{H} = NM_{L} = \frac{3}{8} \left( V_{DD} + \frac{2}{3} V_{th} \right)$$

$NM_{H}$  noise margin for high input

$NM_L$ : noise margin for low input

$V_{th}$ : threshold voltage

Noise margins are typically around 0.4  $V_{DD}$ ; close to half power-supply voltage  $\rightarrow$  CMOS ideal from noise-immunity standpoint

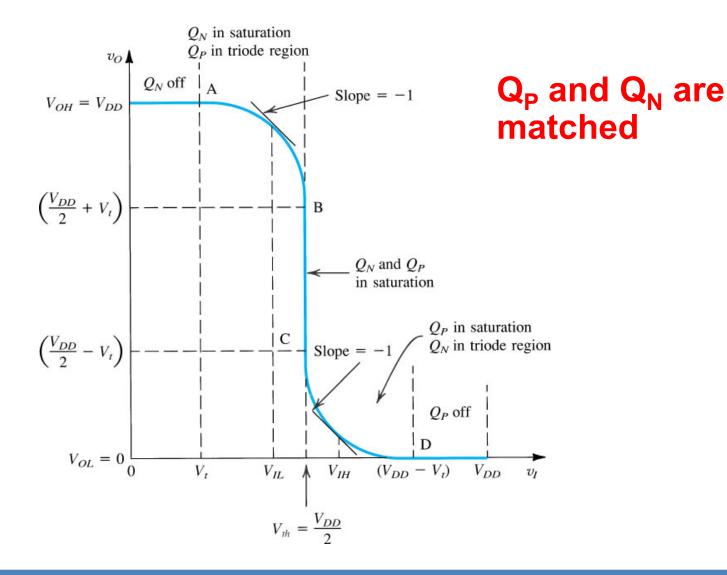

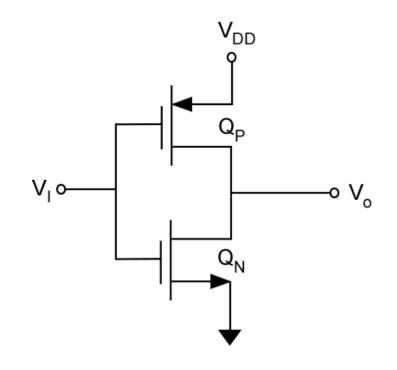

#### **CMOS Inverter VTC**

#### **CMOS Inverter VTC**

#### **Derivation**

- Assume that transistors are matched

- ▶ Vertical segment of VTC is when both Q<sub>N</sub> and Q<sub>P</sub> are saturated

- ightharpoonup No channel length modulation effect ightharpoonup  $\lambda = 0$

- $\triangleright$  Vertical segment occurs at  $v_i = V_{DD}/2$

- $\triangleright V_{IL}$ : maximum permitted logic-0 level of input (slope=-1)

- $\triangleright V_{IH}$ : minimum permitted logic-1 level of input (slope=-1)

To determine  $V_{IH}$ , assume  $Q_N$  in triode region and  $Q_P$  in saturation region

$$(v_I - V_t)v_o - \frac{1}{2}v_o^2 = \frac{1}{2}(V_{DD} - v_I - V_t)^2$$

Next, we differentiate both sides relative to  $v_i$

$$(v_{I} - V_{t}) \frac{dv_{o}}{dv_{I}} + v_{o} - v_{o} \frac{dv_{o}}{dv_{I}} = -(V_{DD} - v_{I} - V_{t})$$

#### **CMOS Inverter VTC**

Substitute  $v_i = V_{IH}$  and  $dv_o/dv_i = -1$

$$v_o = V_{IH} - \frac{V_{DD}}{2}$$

After substitutions, we get

$$V_{IH} = \frac{1}{8} \left( 5V_{DD} - 2V_t \right)$$

Same analysis can be repeated for  $V_{IL}$  to get

$$V_{IL} = \frac{1}{8} (3V_{DD} + 2V_t)$$

## **CMOS Inverter Noise Margins**

$$V_{IH} = \frac{1}{8} \left( 5V_{DD} - 2V_t \right)$$

$$V_{IL} = \frac{1}{8} (3V_{DD} + 2V_t)$$

$$NM_H = \frac{1}{8} \left( 3V_{DD} + 2V_t \right)$$

$$NM_L = \frac{1}{8} \left( 3V_{DD} + 2V_t \right)$$

Symmetry in VTC → equal noise margins

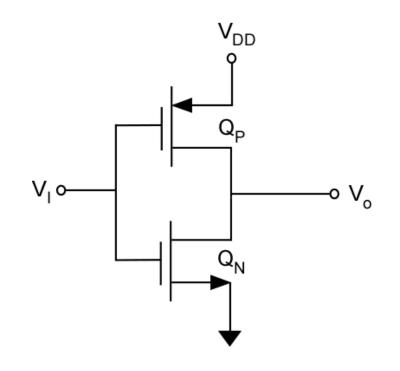

#### **Matched CMOS Inverter VTC**

CMOS inverter can be made to switch at specific threshold voltage by appropriately sizing the transistors

$$\left(\frac{W}{L}\right)_p = \frac{\mu_n}{\mu_p} \left(\frac{W}{L}\right)_n$$

Symmetrical transfer characteristics is obtained via matching → equal current driving capabilities in both directions (pull-up and pull-down)

## VTC and Noise Margins - Problem

An inverter is designed with equal-sized NMOS and PMOS transistors and fabricated in a 0.8-micron CMOS technology for which  $k_n$ ' = 120  $\mu$ A/V²,  $k_p$ ' = 60  $\mu$ A/V²,  $V_{tn} = |V_{tp}| = 0.7$  V,  $V_{DD} = 3$ V,  $L_n = L_p = 0.8$   $\mu$ m,  $W_n = W_p = 1.2$   $\mu$ m, find  $V_{IL}$ ,  $V_{IH}$  and the noise margins.

Equal sizes NMOS and PMOS, but  $k_n'=2k_p'$

$$V_{t} = 0.7 \text{V}$$

For  $V_{IH}$ :  $\mathbf{Q_N}$  in triode and  $\mathbf{Q_P}$  in saturation

$$k'_{n} \left(\frac{W}{L}\right)_{n} \left[ (V_{I} - V_{t}) V_{o} - \frac{1}{2} V_{o}^{2} \right] = \frac{1}{2} k'_{p} \left(\frac{W}{L}\right)_{p} (V_{DD} - V_{I} - V_{t})^{2}$$

$$4(V_I - V_t)V_o - 2V_o^2 = (V_{DD} - V_I - V_t)^2$$

(1)

#### Differentiating both sides relative to $V_I$ results in:

$$\frac{\partial}{\partial V_I}: 4(V_I - V_t) \frac{\partial V_o}{\partial V_I} + 4V_o - 4V_o \frac{\partial V_o}{\partial V_I} = 2(V_{DD} - V_I - V_t)(-1)$$

#### Substitute the values together with:

$$V_I = V_{IH}$$

and  $\frac{\partial V_o}{\partial V_I} = -1$

$$4(V_{IH} - 0.7)(-1) + 4V_o + 4V_o = 2(V_{IH} - 3 + 0.7)$$

$$V_{IH} = \frac{8V_o + 7.4}{6} = 1.33V_o + 1.23 \tag{2}$$

From (1):

$$4(V_{IH} - 0.7)V_o - 2V_o^2 = (3 - V_{IH} - 0.7)^2$$

$$4(V_{IH} - 0.7)V_o - 2V_o^2 = (2.3 - V_{IH})^2$$

(3)

solving (2) & (3):

$$1.55V_o^2 + 4.97V_o - 1.14 = 0$$

$$\Rightarrow V_o = 0.22 V$$

$V_{IH} = 1.52 V$

#### For $V_{IL}$ : $Q_N$ is in saturation and $Q_P$ in triode

$$\frac{1}{2}k_{n}'\left(\frac{W}{L}\right)_{n}(V_{I}-V_{t})^{2}=k_{p}'\left(\frac{W}{L}\right)_{p}\left[(V_{DD}-V_{I}-V_{t})(V_{DD}-V_{o})-\frac{1}{2}(V_{DD}-V_{o})^{2}\right]$$

$$(V_I - 0.7)^2 = (3 - V_I - 0.7)(3 - V_o) - \frac{1}{2}(3 - V_o)^2$$

(1)

$$(V_I - 0.7)^2 = (2.3 - V_I)(3 - V_o) - \frac{1}{2}(3 - V_o)^2$$

$$\frac{\partial}{\partial V_I} \Rightarrow 2(V_I - 0.7) = (2.3 - V_I) \left( -\frac{\partial V_o}{\partial V_I} \right) - (3 - V_o) + (3 - V_o) \frac{\partial V_o}{\partial V_I}$$

$$V_I = V_{IL}$$

and  $\frac{\partial V_o}{\partial V_I} = -1$

$$2V_{IL} - 1.4 = 2.3 - V_{IL} - 3 + V_o + 3 + V_o$$

$$V_{IL} = \frac{2}{3}V_o - 1.15$$

From (1):

$$(V_{IL} - 0.7)^2 = (2.3 - V_{IL})(3 - V_o) - \frac{1}{2}(3 - V_o)^2$$

$$(0.66V_o - 1.85)^2 = (3.45 - 0.66V_o)(3 - V_o) - \frac{1}{2}(3 - V_o)^2$$

$$V_o = 2.96 V$$

$$V_{IL} = 0.81 V$$

#### **Noise Margins:**

$$NM_H = 3 - 1.52 = 1.48 V$$

$$NM_L = 0.81 - 0 = 0.81 V$$

Since  $Q_N$  and  $Q_P$  are not matched, the VTC is not symmetric