# ECE 342 Electronic Circuits

# Lecture 35 CMOS Logic

Jose E. Schutt-Aine

Electrical & Computer Engineering

University of Illinois

jesa@Illinois.edu

### **Digital Logic - Generalization**

De Morgan's Law

$$\overline{A+B+C+...} = \overline{A} \cdot \overline{B} \cdot \overline{C} \cdot ...$$

$$\overline{A \cdot B \cdot C \cdot \dots} = \overline{A} + \overline{B} + \overline{C} + \dots$$

Distributive Law

$$AB + AC + BC + BD = A(B+C) + B(C+D)$$

#### General Procedure

- 1. Design PDN to satisfy logic function

- 2. Construct PUN to be complementary of PDN in every way

- 3. Optimize using distributive rule

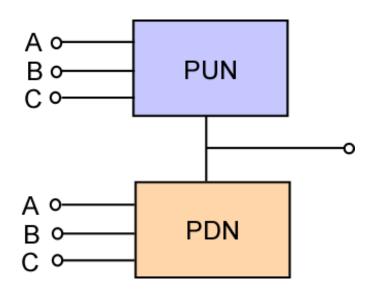

### **CMOS Logic Gate Circuits**

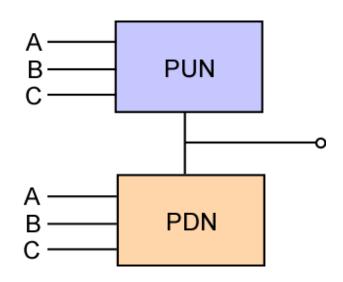

- Two Networks

- Pull-down network (PDN) with NMOS

- Pull-up network (PUN) with PMOS

PUN conducts when inputs are low and consists of PMOS transistors

PDN consists of NMOS transistors and is active when inputs are high

- PDN and PUN utilize devices

- In parallel to form OR functions

- In series to form AND functions

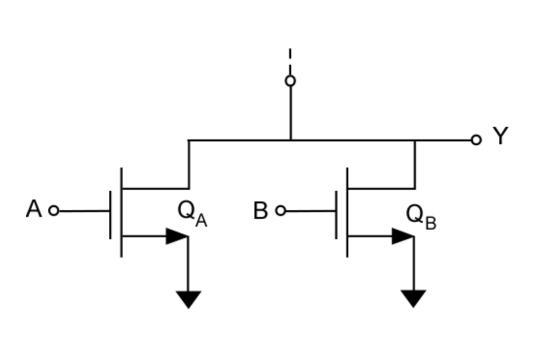

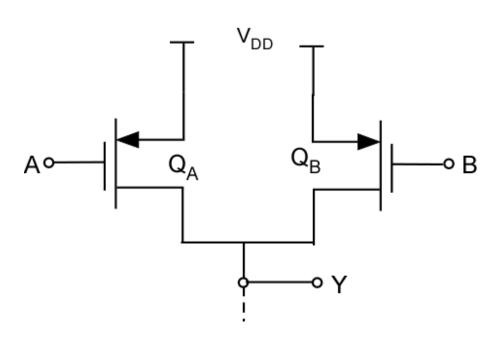

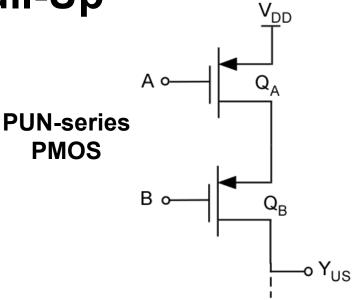

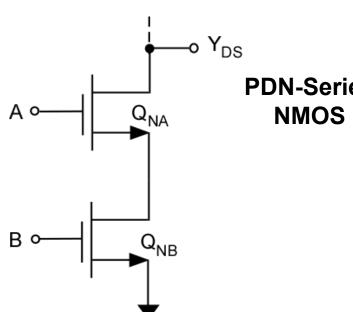

### **Pull-Down Networks**

$$\overline{Y} = A + B$$

$$\overline{Y} = AB$$

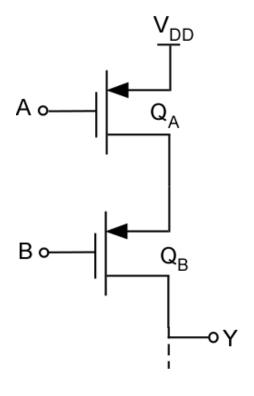

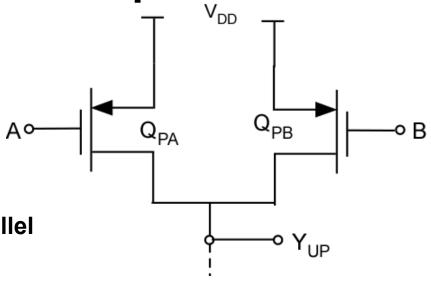

### **Pull-Up Networks**

$$Y = \overline{A} + \overline{B}$$

$$Y = \overline{A}\overline{B}$$

## **Basic Logic Function**

| Basic<br>Function | INVERTER      | NOR                     | NAND                    |

|-------------------|---------------|-------------------------|-------------------------|

| Symbol            | AY            | A                       | A                       |

| # Devices<br>PUN  | 1<br>PMOS     | 2<br>PMOS-Series        | 2<br>PMOS-Parallel      |

| # Devices<br>PDN  | 1<br>NMOS     | 2<br>NMOS-Parallel      | 2<br>NMOS-Series        |

| Truth<br>Table    | A Y 0 1 1 1 0 | A B Y 0 0 1 0 1 0 1 0 0 | A B Y 0 0 1 0 1 1 1 0 1 |

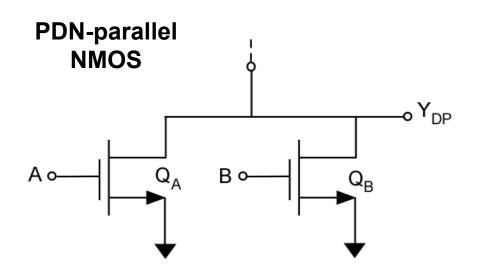

### **Pull-Down and Pull-Up Functions**

Pull-up network (PUN)

**Pull-down network (PDN)**

- Key features

- When PDN switch is on, PUN switch is off and vice versa

- Conditions for being on and off are complementary

$$Y_{DP} = \overline{A + B}$$

| Α | В | Y <sub>DP</sub> |

|---|---|-----------------|

| 0 | 0 | 1               |

| 0 | 1 | 0               |

| 1 | 0 | 0               |

| 1 | 1 | 0               |

### **Truth Tables**

$$\begin{array}{c|cccc} Y_{US} = AB & & \\ \hline & A & B & Y_{US} \\ \hline & 0 & 0 & 1 \\ & 0 & 1 & 0 \\ & 1 & 0 & 0 \\ & 1 & 1 & 0 \\ \end{array}$$

When  $Y_{DP}$  in PDN-parallel is low, this means that either A or B (or both) is high. When either A or B (or both) is high, either transistor (or both) in PUNseries are off  $Y_{US}$  = low

When  $Y_{DP}$  in PDN-parallel is high, both A and B are low. Both transistors in PUN-Series are on creating a path to VDD.  $Y_{US}$ =high $\rightarrow Y_{US}$ = $Y_{DP}$ .

PDN-Parallel and PUN-series are complementary

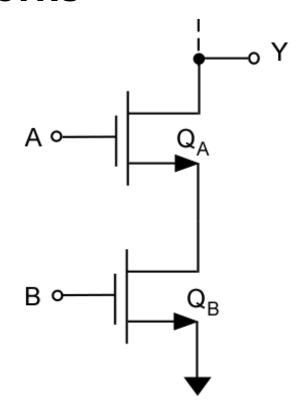

| <b>T</b> 7 |   | AD |

|------------|---|----|

| Y          | _ | AB |

| 1 Da       |   | D  |

| 128        |   |    |

| Α | В | Y <sub>DS</sub> |

|---|---|-----------------|

| 0 | 0 | 1               |

| 0 | 1 | 1               |

| 1 | 0 | 1               |

| 1 | 1 | 0               |

**Truth Tables**

$$Y_{UP} = \overline{A} + \overline{B}$$

| Α | В | Y <sub>UP</sub> |

|---|---|-----------------|

| 0 | 0 | 1               |

| 0 | 1 | 1               |

| 1 | 0 | 1               |

| 1 | 1 | 0               |

If  $Y_{DS}$  is low, both A and B must be high in which case both transistors in PUN-Parallel are off providing no path to  $V_{DD} \rightarrow Y_{UP} = Iow \rightarrow Y_{UP} = Y_{DS}$ .

If  $Y_{DS}$  is high, then either A or B (or both) are off (low) in which case either  $Q_{PA}$  or  $Q_{PB}$  in PUN-Parallel will be on and present a path to  $V_{DD}$ ; thus  $Y_{UP}$ =high  $\Rightarrow Y_{UP}$ = $Y_{DS}$

### **PDN-Series and PUN-Parallel are complementary**

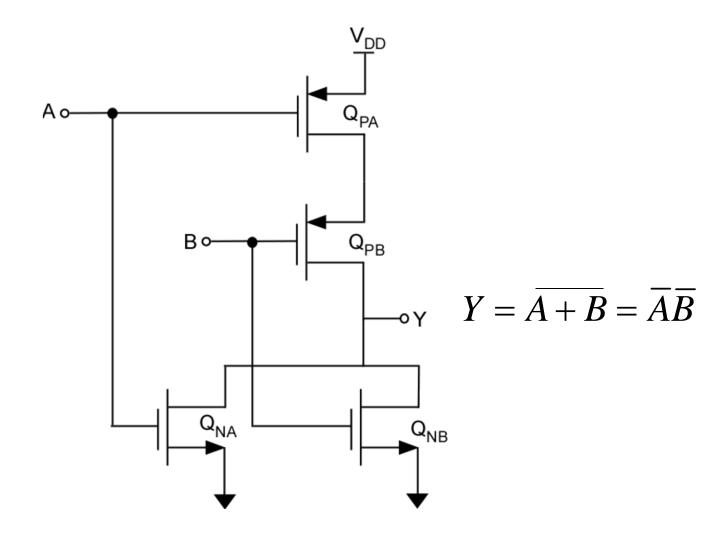

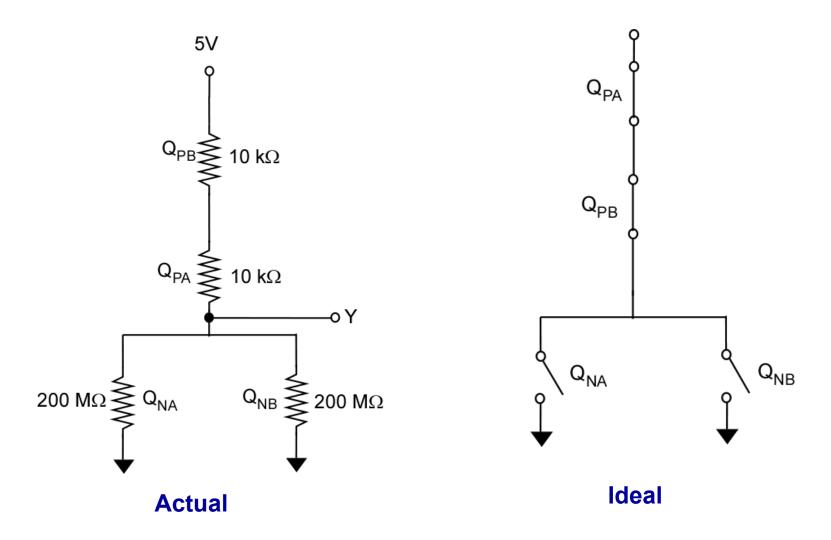

### **Two-Input NOR Gate**

### **Two-Input NOR Gate**

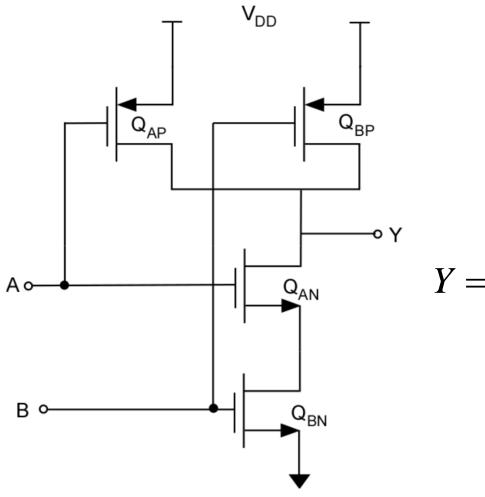

## **Two-Input NAND Gate**

$$Y = \overline{AB} = \overline{A} + \overline{B}$$

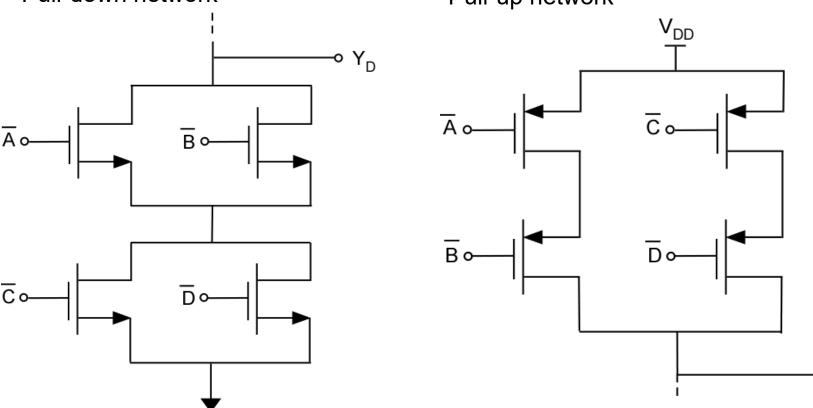

### **Example**

$$Y = A\overline{B} \cdot \overline{CD}$$

Using De Morgan's Law

$$Y = A\overline{B} \cdot \overline{CD} = AB + CD = (\overline{A} + \overline{B}) \cdot (\overline{C} + \overline{D})$$

Pull-down network

Pull-up network

۰Υ

### **Example 1**

**Evaluate Logic Function**

$$Y = (\overline{A + \overline{B}})C$$

from pull down

$$Y = \overline{A}B + \overline{C}$$

from pull up

$$\overline{A}B + \overline{C} = \overline{\overline{A}B \cdot C} = \overline{(A + \overline{B})C}$$

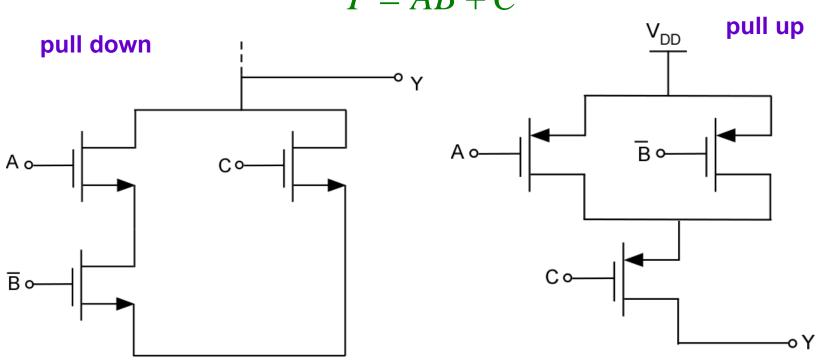

### Example 2

Implement the function

$$\overline{Y} = A\overline{B} + C$$

$$Y = \overline{A\overline{B} + C} = \overline{A\overline{B} \cdot C} = (\overline{A} + B) \cdot \overline{C}$$

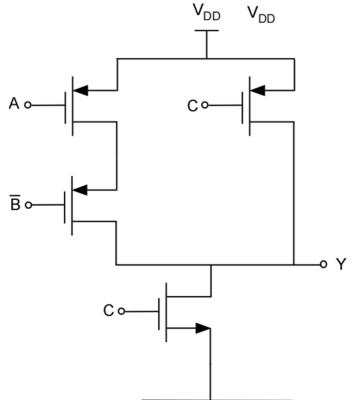

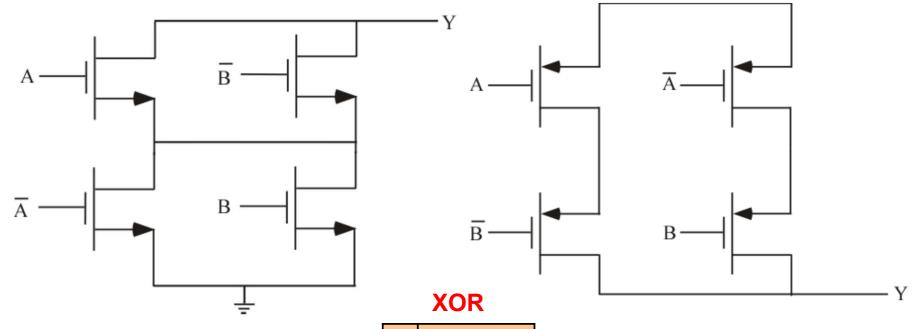

### **Exclusive-OR (XOR) Function**

$$Y = A\overline{B} + \overline{A}B$$

$\overline{Y} = (\overline{A} + B)(A + \overline{B})$

pull down

|   | Α | В | Υ |

|---|---|---|---|

| I | 0 | 0 | 0 |

| ١ | 0 | 1 | 1 |

| ١ | 1 | 0 | 1 |

|   | 1 | 1 | 0 |

pull up

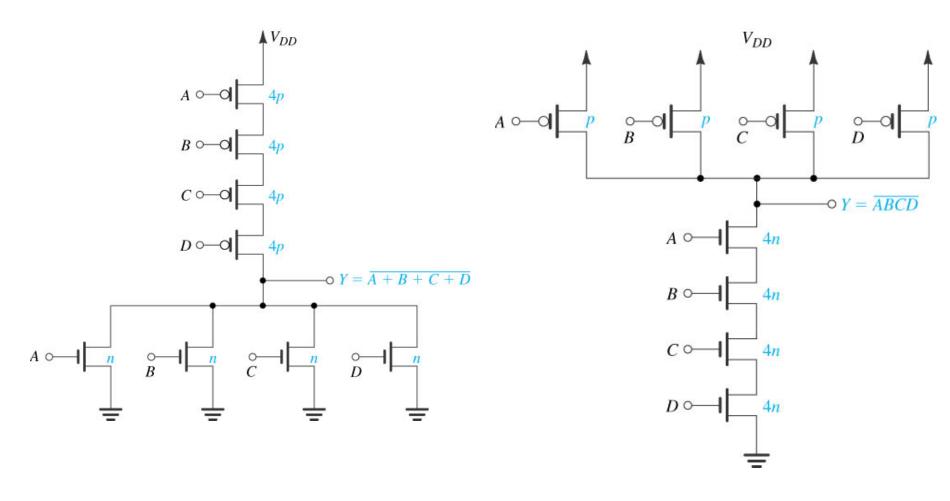

### **Transistor Sizing**

#### **Objectives**

- PDN provides discharge current of at least that of an NMOS

- > PUN provides charging current of at least that of a PMOS

- Worst case gate delay equal to that of basic inverter

- Find combination that results in lowest output current

- > For transistors in parallel aspect ratios add

- > For transistors in series, inverses of aspect ratios add

Series:

$$\frac{1}{(W/L)_{eq}} = \frac{1}{(W/L)_{1}} + \frac{1}{(W/L)_{2}} + ... + \frac{1}{(W/L)_{M}}$$

Parallel:

$$(W/L)_{eq} = (W/L)_1 + (W/L)_2 + ... + (W/L)_M$$

$$p = (W/L)_p$$

$n = (W/L)_n$

### **Transistor Sizing**

**NOR**

**NAND**

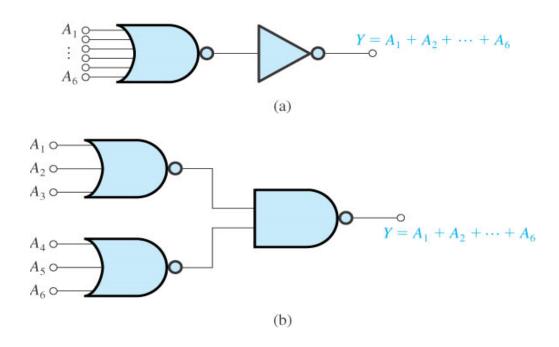

### **Transistor Sizing – Example 1**

Two approaches to realizing the OR function of six input variables. Assuming that the transistors in both circuits are properly sized to provide each gate with a current-driving capability equal to that of the basic matched inverter, find the number of transistors and the total area of each circuit. Assume the basic inverter to have a  $(W/L)_n$  ratio of 1.2  $\mu$ m/0.8  $\mu$ m and a  $(W/L)_p$  ratio of 3.6  $\mu$ m/0.8  $\mu$ m.

### **Transistor Sizing – Example 1**

For design (a), there are 2(6)+2=14 transistors:

All 7 NMOS use  $(W/L)_n = n$

1 PMOS uses  $(W/L)_p = p$

6 PMOS use  $(W/L)_p = 6p$

Total Area =  $7(1.2)0.8 + 1(3.6)0.8 + 6(6)(3.6)0.8 = 113.3 \mu m^2$

For design (b), there are 2(3)2 + 1(2)2=16 transistors:

6 NMOS use  $(W/L)_n = n$

6 PMOS use  $(W/L)_p = 3p$

2 PMOS use  $(W/L)_p = p$

2 NMOS use  $(W/L)_n = 2n$

Total Area =  $70(1.2)0.8 = 67.2 \mu m^2$ , or 59% of (a)